Introducción: Las Conexiones Verticales Que Definen Tu Diseño

Las vías son las interconexiones verticales que permiten que las señales, la alimentación y los planos de tierra se comuniquen entre las distintas capas de una PCB. Sin ellas, cualquier placa multicapa sería simplemente un apilado de circuitos aislados e inútiles.

Aunque parecen un detalle menor — simples agujeros taladrados y metalizados — la elección del tipo de vía, su tamaño y su ubicación impactan directamente en la integridad de señal, la capacidad de fabricación, el coste y la fiabilidad del producto final.

Si está comparando opciones de fabricación, también conviene revisar nuestro servicio de fabricación de PCB, el servicio de montaje PCBA y el calculador de PCB para validar costes, stack-up y viabilidad antes de liberar producción.

Hommer Zhao, Fundador & Experto Técnico: "He revisado más de 3.000 diseños de clientes y el error más frecuente con las vías no es técnico, sino de comunicación: el diseñador especifica blind vias sin confirmar que su fabricante las soporta, y el proyecto se retrasa dos semanas mientras se rediseña."

En esta guía cubrimos los cuatro tipos principales de vías, las reglas DFM críticas que tu fabricante evalúa, una comparativa de costes real, y los errores más comunes que debes evitar.

---

¿Qué Es una Vía en PCB y Cómo Funciona?

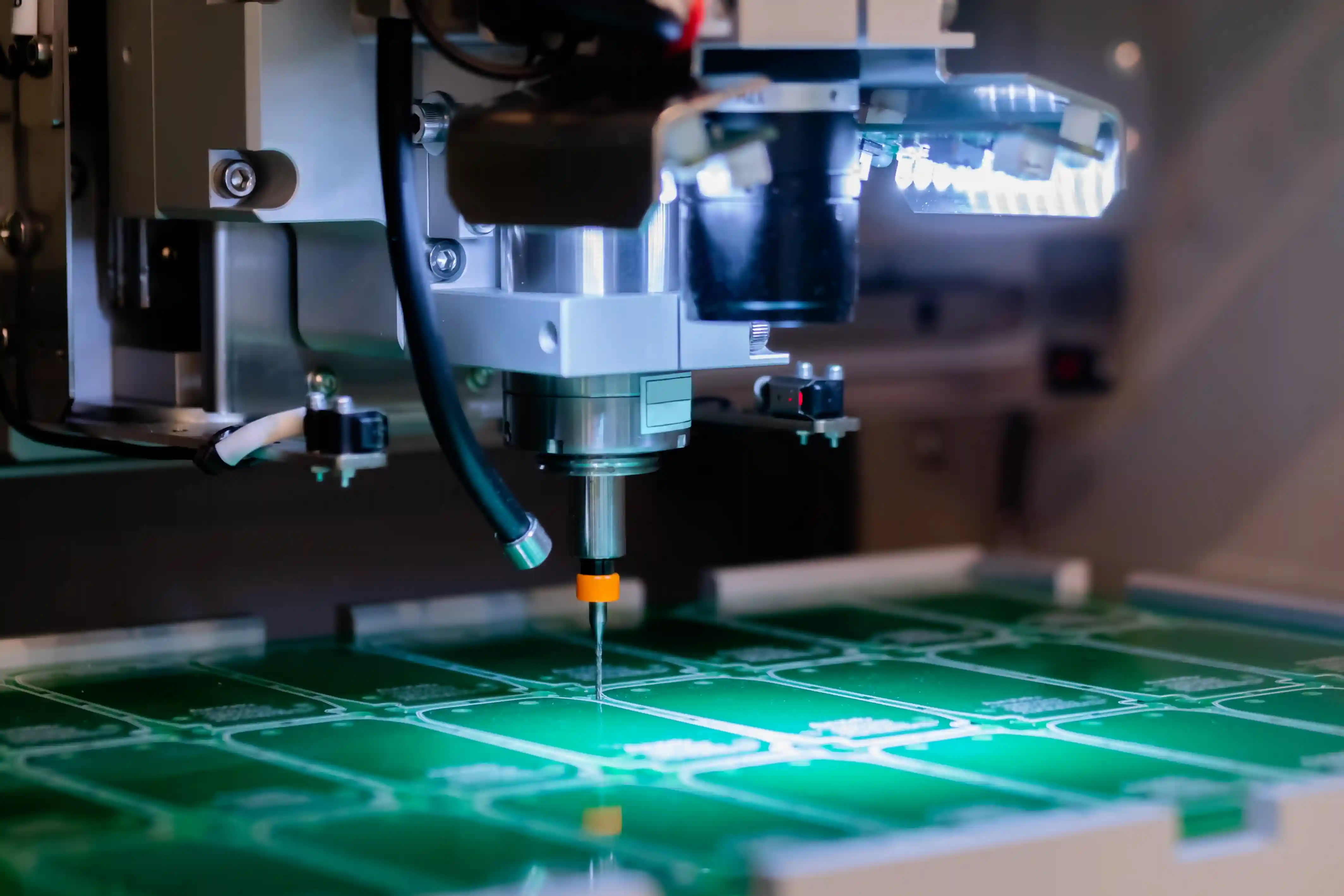

Una vía (del inglés via, abreviatura de vertical interconnect access) es un orificio taladrado en la PCB cuyas paredes internas se recubren con cobre electrolítico. Este recubrimiento crea un conducto eléctrico que conecta pistas o planos de cobre en diferentes capas.

Anatomía de una Vía

| Componente | Descripción |

|---|---|

| Drill hole (orificio) | El agujero perforado mecánica o lásermente. Su diámetro define la capacidad de corriente y la relación de aspecto |

| Barrel (barril) | La pared cilíndrica de cobre depositado que proporciona la conductividad entre capas |

| Pad (pad) | El anillo de cobre en las capas externas que rodea el orificio, conectándose a las pistas |

| Anillo anular | La distancia entre el borde del orificio y el borde exterior del pad — parámetro DFM crítico |

| Antipad (clearance) | La zona sin cobre alrededor de la vía en las capas de plano donde la vía no debe conectarse |

El proceso de metalización utiliza cobre electrolítico depositado con un espesor típico de 20-25 µm en las paredes del barrel, garantizando una resistencia de contacto inferior a 5 mΩ por vía.

---

Los 4 Tipos Principales de Vías

1. Through-Hole Via (Vía Pasante) — El Estándar Universal

La vía pasante atraviesa todas las capas de la PCB, desde la cara superior hasta la inferior. Es el tipo más simple, económico y fiable.

Características técnicas:

| Parámetro | Valor típico |

|---|---|

| Diámetro mínimo de taladro | 0,20 mm (8 mil) mecánico |

| Relación de aspecto máxima | 8:1 (espesor placa : diámetro taladro) |

| Pad mínimo | Drill + 0,30 mm |

| Anillo anular mínimo (IPC Clase 2) | 0,15 mm (6 mil) |

| Coste relativo | Baseline (1x) |

Cuándo usarla: En el 90% de los diseños de 2 a 6 capas donde no hay restricciones severas de espacio ni routing de alta densidad.

Limitación: Ocupa espacio en todas las capas, incluso en aquellas donde no se necesita conexión, lo que consume área de routing útil.

2. Blind Via (Vía Ciega) — Conexión Parcial desde una Cara

La vía ciega conecta una capa externa (top o bottom) con una o más capas internas, sin atravesar toda la placa. Es visible solo desde un lado.

Características técnicas:

| Parámetro | Valor típico |

|---|---|

| Diámetro mínimo de taladro | 0,10 mm (4 mil) láser; 0,15 mm mecánico |

| Relación de aspecto máxima | 1:1 (profundidad : diámetro) |

| Profundidad típica | 1-2 capas |

| Coste relativo | 1,3x – 1,5x vs through-hole |

Cuándo usarla: En diseños HDI donde necesitas liberar espacio de routing en capas internas, o bajo componentes BGA con pitch fino.

Ejemplo de notación: L1-L2 (conecta capa 1 con capa 2) o L1-L3 (capa 1 a capa 3).

3. Buried Via (Vía Enterrada) — Oculta en el Interior

La vía enterrada conecta únicamente capas internas entre sí, sin llegar a ninguna cara externa. No es visible tras la laminación final.

Características técnicas:

| Parámetro | Valor típico |

|---|---|

| Diámetro mínimo de taladro | 0,10 mm – 0,15 mm |

| Relación de aspecto máxima | 8:1 (en sub-laminados) |

| Coste relativo | 1,4x – 1,7x vs through-hole |

Cuándo usarla: En placas multicapa de 8+ capas donde las capas internas necesitan interconexiones sin sacrificar espacio en las caras externas. Frecuente en diseños para telecomunicaciones y automoción.

Hommer Zhao, Fundador & Experto Técnico: "Las vías enterradas son las más caras de fabricar porque requieren taladrar y metalizar sub-laminados antes de la laminación final. He visto diseños donde se usaban 200 buried vias cuando se podían resolver con 50 through-hole vias y un routing más inteligente. Siempre pregunto al diseñador: ¿realmente necesitas esas vías enterradas, o puedes optimizar el stackup?"

4. Microvía — La Clave del HDI

Las microvías son orificios de diámetro ≤ 150 µm (típicamente 75-100 µm) taladrados con láser. Son el componente fundamental de las PCB HDI (High Density Interconnect).

Características técnicas:

| Parámetro | Valor típico |

|---|---|

| Diámetro de taladro | 0,075 – 0,15 mm (3-6 mil) |

| Profundidad | 1 capa (máx. 2 para stacked) |

| Relación de aspecto máxima | 0,75:1 (recomendado) |

| Pad típico | 0,25 – 0,35 mm |

| Coste relativo | 1,5x – 2,5x vs through-hole |

Cuándo usarla: Bajo componentes BGA de pitch ≤ 0,5 mm, diseños flex-PCB de alta densidad, y aplicaciones donde el tamaño es crítico (wearables, smartphones, dispositivos médicos).

---

Comparativa de Costes: ¿Cuánto Cuesta Cada Tipo de Vía?

El coste de fabricación varía significativamente según el tipo de vía. Los procesos de taladrado representan hasta el 40% del coste total de fabricación de una PCB[5].

| Tipo de Vía | Incremento de Coste | Proceso de Taladrado | Pasos Adicionales | Caso de Uso Óptimo |

|---|---|---|---|---|

| Through-hole | Baseline | Mecánico (1 paso) | Ninguno | 90% de diseños estándar |

| Blind | +30-50% | Láser o mecánico controlado | Laminación secuencial | HDI, BGA escape routing |

| Buried | +40-70% | Mecánico en sub-laminados | Laminación múltiple + taladrado | Placas 8+ capas complejas |

| Microvía | +50-150% | Láser (CO2 o UV) | Llenado con resina, planarización | Pitch ≤ 0,5 mm, wearables |

Datos Clave de Coste

- El coste del láser se concentra en el setup, no en la cantidad: taladrar 1 o 100 microvías tiene un coste similar por panel[5]

- Las buried vias pueden incrementar el coste por pulgada cuadrada de $1-5 a $2-10[5]

- Un diseño inteligente con blind vias puede reducir el coste total al permitir menos capas (una placa de 8 capas con blind vias puede reemplazar una de 10 capas con solo through-holes)

---

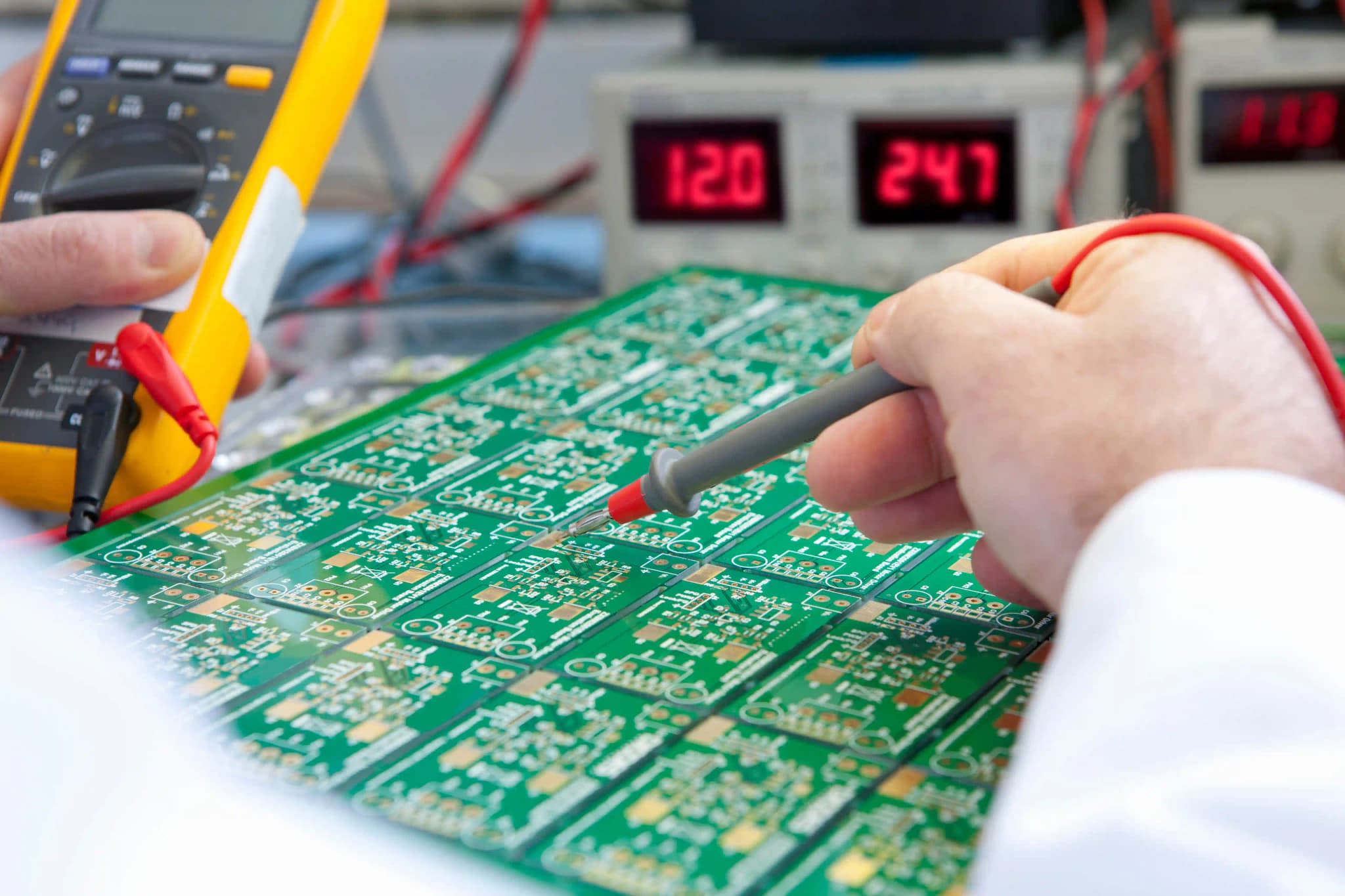

Reglas DFM Críticas para Vías

Tu fabricante evalúa estos parámetros al recibir tu diseño. Incumplir cualquiera de ellos generará una consulta DFM y un posible rediseño.

1. Relación de Aspecto (Aspect Ratio)

La relación entre el espesor de la placa y el diámetro del orificio determina si el cobre electrolítico puede depositarse uniformemente en las paredes del barrel.

| Tipo de Vía | Aspect Ratio Máximo | Ejemplo |

|---|---|---|

| Through-hole (estándar) | 8:1 | Placa 1,6 mm → drill mín. 0,20 mm |

| Through-hole (alta fiabilidad) | 6:1 | Placa 1,6 mm → drill mín. 0,27 mm |

| Blind via | 1:1 | Profundidad 0,2 mm → drill mín. 0,20 mm |

| Microvía | 0,75:1 (recomendado) | Profundidad 0,1 mm → drill mín. 0,13 mm |

¿Qué pasa si excedes la ratio? El cobre no llega al fondo del barrel, creando un punto de alta resistencia o una desconexión intermitente que solo aparece bajo estrés térmico[1].

2. Anillo Anular (Annular Ring)

El anillo anular es la distancia entre el borde del orificio taladrado y el borde exterior del pad de cobre. Si es demasiado estrecho, el taladro puede "romper" el pad (via breakout), eliminando la conexión eléctrica.

| Clase IPC | Anillo Anular Mínimo (externas) | Anillo Anular Mínimo (internas) |

|---|---|---|

| Clase 1 (productos generales) | 0,05 mm (2 mil) | 0,025 mm (1 mil) |

| Clase 2 (productos dedicados) | 0,15 mm (6 mil) | 0,05 mm (2 mil) |

| Clase 3 (alta fiabilidad) | 0,20 mm (8 mil) | 0,10 mm (4 mil) |

Fórmula práctica para pad size:

Pad diameter = Drill diameter + (2 × Anillo anular mínimo) + Tolerancia de registro

Para diseños estándar (Clase 2): Pad = Drill + 0,30 mm proporciona un margen seguro[3].

3. Espaciado Via-a-Via

El espaciado mínimo entre vías evita cortocircuitos durante el proceso de metalización y problemas de aislamiento.

| Escenario | Espaciado Mínimo |

|---|---|

| Via-a-via (estándar) | 0,25 mm (10 mil) |

| Via-a-pista | 0,20 mm (8 mil) |

| Microvía-a-microvía | 0,15 mm (6 mil) |

| Via-a-borde de placa | 0,50 mm (20 mil) |

4. Via-in-Pad (Vía en el Pad)

Colocar una vía directamente en un pad SMD es una técnica avanzada que ahorra espacio pero requiere un proceso adicional: la vía debe ser llenada con resina epoxi y planarizada para que la superficie quede plana antes de la soldadura.

| Parámetro | Requisito |

|---|---|

| Llenado de vía | Resina epoxi (IPC-4761 Tipo VII) |

| Planarización | ≤ 25 µm de altura/depresión |

| Coste adicional | +15-25% sobre vía estándar |

| Alternativa | Via-in-pad "tented" (cubierta con solder mask, sin rellenar) |

¿Cuándo es necesaria? En pads de componentes BGA, QFN y LGA donde no hay espacio para sacar la vía con un dog-bone (pista corta) hacia fuera del pad.

---

Vías Apiladas vs Escalonadas en HDI

En diseños HDI con múltiples niveles de microvías, existen dos estrategias de interconexión:

Vías Apiladas (Stacked)

Las microvías se colocan directamente una sobre otra, formando una columna vertical a través de múltiples capas.

Ventajas:

- Máximo ahorro de espacio

- Ruta eléctrica más corta (menor inductancia)

- Ideal para escape routing de BGA ultra-densos

Desventajas:

- Coste de fabricación +20-30% vs escalonadas[4]

- Mayor concentración de estrés termomecánico

- Limitación práctica: máximo 2 niveles de microvías apiladas para mantener fiabilidad

Vías Escalonadas (Staggered)

Las microvías se desplazan lateralmente entre niveles, evitando la superposición directa.

Ventajas:

- Distribución más uniforme del estrés térmico

- Mayor fiabilidad a largo plazo

- Coste de fabricación más predecible

Desventajas:

- Consume más espacio lateral

- Ruta eléctrica ligeramente más larga

Tabla Comparativa

| Criterio | Apiladas (Stacked) | Escalonadas (Staggered) |

|---|---|---|

| Densidad de routing | Máxima | Alta |

| Fiabilidad térmica | Menor (concentración de estrés) | Mayor (distribución uniforme) |

| Coste | +20-30% | Baseline HDI |

| Niveles máximos recomendados | 2 | 3-4 |

| Aplicación ideal | Smartphones, wearables | Automoción, médico, aeroespacial |

Hommer Zhao, Fundador & Experto Técnico: "Mi recomendación para el 80% de diseños HDI es usar vías escalonadas. Solo recurro a apiladas cuando el pitch del BGA es inferior a 0,4 mm y no hay otra forma de sacar las señales. La fiabilidad siempre debe primar sobre la densidad."

---

7 Errores Comunes en el Diseño de Vías

Estos son los errores que más frecuentemente generan consultas DFM o fallos en producción:

Error 1: Especificar Blind/Buried Vias Sin Verificar Capacidad del Fabricante

Problema: No todos los fabricantes pueden producir vías ciegas o enterradas. Muchos fabricantes de bajo coste solo soportan through-hole.

Solución: Antes de diseñar, solicita las design rules de tu fabricante y confirma qué tipos de vías soporta. En PlacaPCB proporcionamos nuestras capacidades de fabricación antes de que inicies el diseño.

Error 2: Exceder la Relación de Aspecto

Problema: Un drill de 0,15 mm en una placa de 2,0 mm da una ratio de 13,3:1 — muy por encima del máximo de 8:1.

Solución: Calcula siempre: Aspect Ratio = Espesor placa ÷ Diámetro drill. Si excedes el límite, aumenta el diámetro del drill o reduce el espesor de la placa.

Error 3: Anillo Anular Insuficiente

Problema: Un pad de 0,40 mm con un drill de 0,30 mm deja solo 0,05 mm de anillo anular — insuficiente para IPC Clase 2.

Solución: Usa la fórmula Pad = Drill + 0,30 mm como mínimo. Para alta fiabilidad, usa Pad = Drill + 0,40 mm.

Error 4: Via-in-Pad Sin Especificar Llenado

Problema: Colocar vías en pads SMD sin especificar que deben ser llenadas y planarizadas causa que la soldadura fluya por la vía durante el reflujo, creando juntas de soldadura insuficientes o vacías.

Solución: Si usas via-in-pad, especifica en tus notas de fabricación: "Vías en pad: rellenar con resina epoxi y planarizar según IPC-4761 Tipo VII".

Error 5: Ignorar el Impacto en la Integridad de Señal

Problema: Las vías introducen inductancia parasitaria y discontinuidades de impedancia en señales de alta velocidad. Un stub de vía (la porción no utilizada del barrel en una through-hole via) puede causar reflexiones significativas por encima de 3 GHz.

Solución: Para señales de alta velocidad, usa back-drilling (eliminar el stub no utilizado) o utiliza blind/buried vias que solo conecten las capas necesarias.

Error 6: Demasiadas Vías en Planos de Alimentación

Problema: Un exceso de vías en un plano de tierra o alimentación crea "queso suizo" — agujeros que fragmentan el plano y aumentan la impedancia del retorno de corriente.

Solución: Mantén las vías de señal agrupadas y alineadas. Evita dispersar vías aleatoriamente en planos de alimentación. Usa herramientas de simulación para verificar la integridad del plano.

Error 7: No Considerar el Thermal Relief en Vías de Plano

Problema: Una vía conectada directamente a un plano de cobre grande sin thermal relief es prácticamente imposible de soldar a mano — el plano actúa como un disipador masivo.

Solución: Configura thermal relief pads (conexiones en cruz) para vías que necesiten soldadura manual o rework. Solo usa conexión directa (sin thermal relief) para vías de corriente alta o retorno de tierra crítico.

---

Guía de Selección: ¿Qué Tipo de Vía Necesitas?

| Tu Escenario | Tipo Recomendado | Justificación |

|---|---|---|

| PCB de 2-4 capas, diseño estándar | Through-hole | Más económica, máxima fiabilidad |

| PCB de 6+ capas, BGA con pitch ≥ 0,65 mm | Through-hole + dog-bone | Suficiente espacio para fan-out |

| PCB de 6+ capas, BGA con pitch 0,5 mm | Blind vias + through-hole | Libera routing en capas internas |

| PCB HDI, BGA con pitch ≤ 0,4 mm | Microvías (apiladas o escalonadas) | Única opción viable para fan-out |

| PCB de 8+ capas, señales internas complejas | Buried vias | Conecta capas internas sin desperdiciar espacio externo |

| Prototipo rápido con presupuesto limitado | Solo through-hole | Minimiza coste y tiempo de entrega |

---

Especificaciones Clave por Norma IPC

| Parámetro | IPC Clase 1 | IPC Clase 2 | IPC Clase 3 |

|---|---|---|---|

| Anillo anular mín. (externas) | 0,05 mm | 0,15 mm | 0,20 mm |

| Anillo anular mín. (internas) | 0,025 mm | 0,05 mm | 0,10 mm |

| Via breakout permitido | Sí (hasta 90°) | Sí (hasta 90°) | No permitido |

| Espesor cobre en barrel | ≥ 18 µm | ≥ 20 µm | ≥ 25 µm |

| Backfill para via-in-pad | No requerido | Recomendado | Obligatorio |

Estas especificaciones están documentadas en la norma IPC-6012 (Qualification and Performance Specification for Rigid PCBs) y deben ser verificadas con tu fabricante para confirmar sus capacidades reales.

---

Preguntas Frecuentes (FAQ)

¿Cuál es el diámetro mínimo de vía que puedo usar?

Para taladrado mecánico, el mínimo práctico es 0,20 mm (8 mil). Con taladrado láser (microvías), se puede llegar a 0,075 mm (3 mil), aunque 0,10 mm (4 mil) es más común y fiable. Consulta las capacidades específicas de tu fabricante de PCB antes de diseñar.

¿Las blind vias son siempre más caras que las through-hole?

Sí, el incremento típico es del 30-50% debido al proceso de laminación secuencial. Sin embargo, si las blind vias te permiten reducir el número de capas (por ejemplo, pasar de 10 a 8 capas), el coste total puede ser menor que el diseño original con solo through-hole vias[5].

¿Cuántas microvías puedo apilar de forma fiable?

La recomendación de la industria es un máximo de 2 niveles de microvías apiladas. Más allá de 2 niveles, el riesgo de fallos por estrés termomecánico aumenta significativamente. Para 3+ niveles, usa vías escalonadas (staggered)[4].

¿Necesito via-in-pad para todos los componentes BGA?

No necesariamente. Para BGAs con pitch ≥ 0,65 mm, puedes usar la técnica de dog-bone (sacar una pista corta del pad y colocar la vía fuera). Via-in-pad es necesaria cuando el pitch es ≤ 0,5 mm y no hay espacio físico para el dog-bone.

¿Cómo afectan las vías a la integridad de señal en alta velocidad?

Las vías introducen inductancia parasitaria (típicamente 0,5-1,5 nH por vía) y discontinuidades de impedancia. Para señales > 3 GHz, los stubs de las through-hole vias causan reflexiones significativas. Las soluciones incluyen back-drilling, usar blind vias, o diseñar con materiales de alta frecuencia como Rogers.

¿Qué información sobre vías debo incluir en mis archivos de fabricación?

Tu paquete de fabricación debe incluir: archivo de taladros Excellon con coordenadas y diámetros, tabla de taladros (drill chart) indicando tipos (PTH, NPTH, blind, buried), notas de fabricación especificando via-in-pad fill requirements, y el stackup detallado mostrando qué capas conecta cada tipo de vía.

---

Conclusión: Diseña las Vías Correctas Desde el Primer Día

La elección del tipo de vía no es una decisión que debas tomar al final del diseño — es una decisión arquitectónica que debe alinearse con tu stackup, tus componentes y tu presupuesto desde el primer esquemático.

Para la mayoría de proyectos, las through-hole vias siguen siendo la opción más fiable y económica. Reserva las blind, buried y microvías para los casos donde realmente las necesitas: alta densidad, BGAs de pitch fino y diseños donde el espacio es el factor limitante.

¿Necesitas ayuda para optimizar las vías de tu diseño? Nuestro equipo de ingeniería revisa tu Gerber gratuitamente y te recomienda la estrategia de vías más eficiente para tu proyecto. Solicita una revisión DFM gratuita →

---